### Al Driving Chips, and Chips Driving Al: An Insider's Perspective on Moore's Law

#### **Trent McConaghy**

Co-founder & CTO, Solido Design Automation Inc.

Singularity Meets Self-Improvement Berlin, October 2013

# Resolution of **Noninvasive Brain Scanning**

Logarithmic Plot

Year

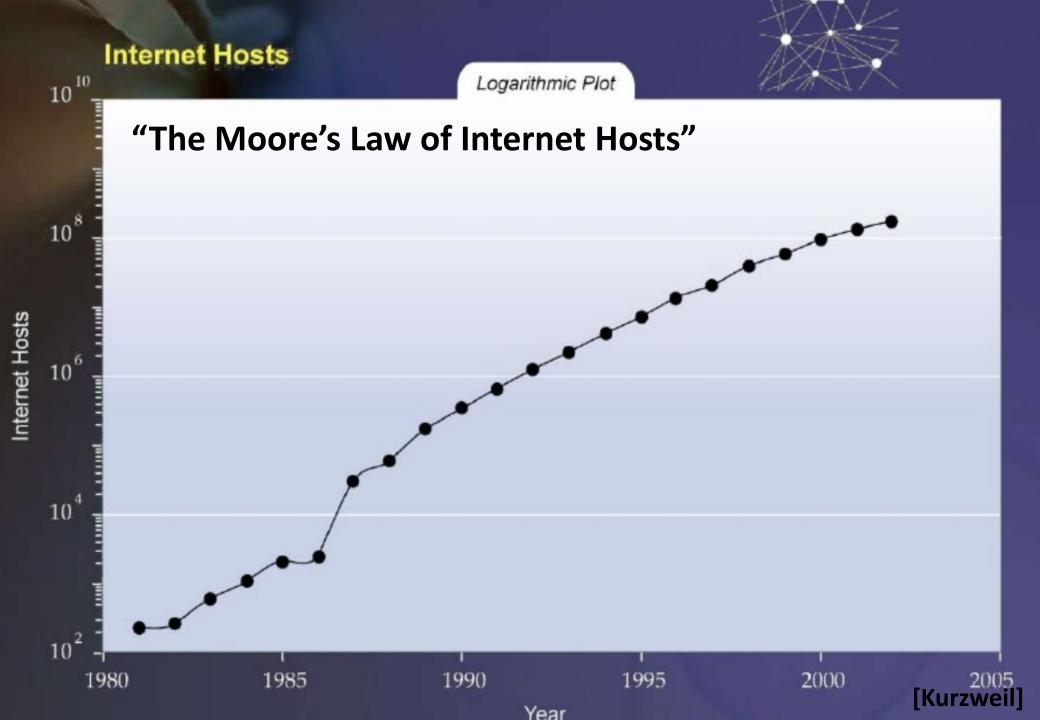

#### "The Moore's Law of Brain Scanning"

0.1

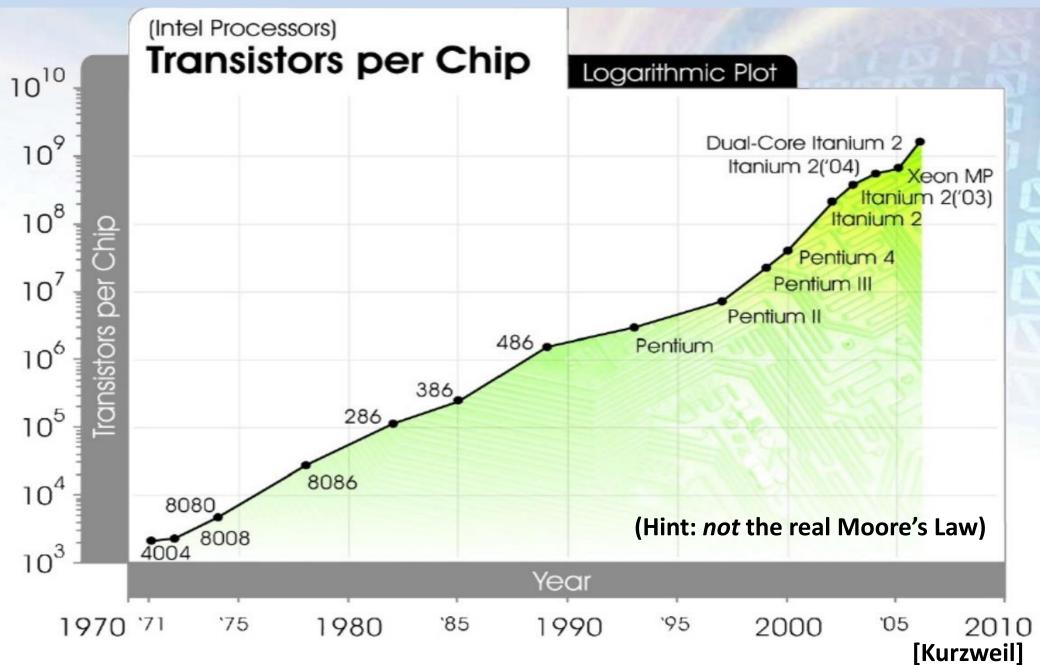

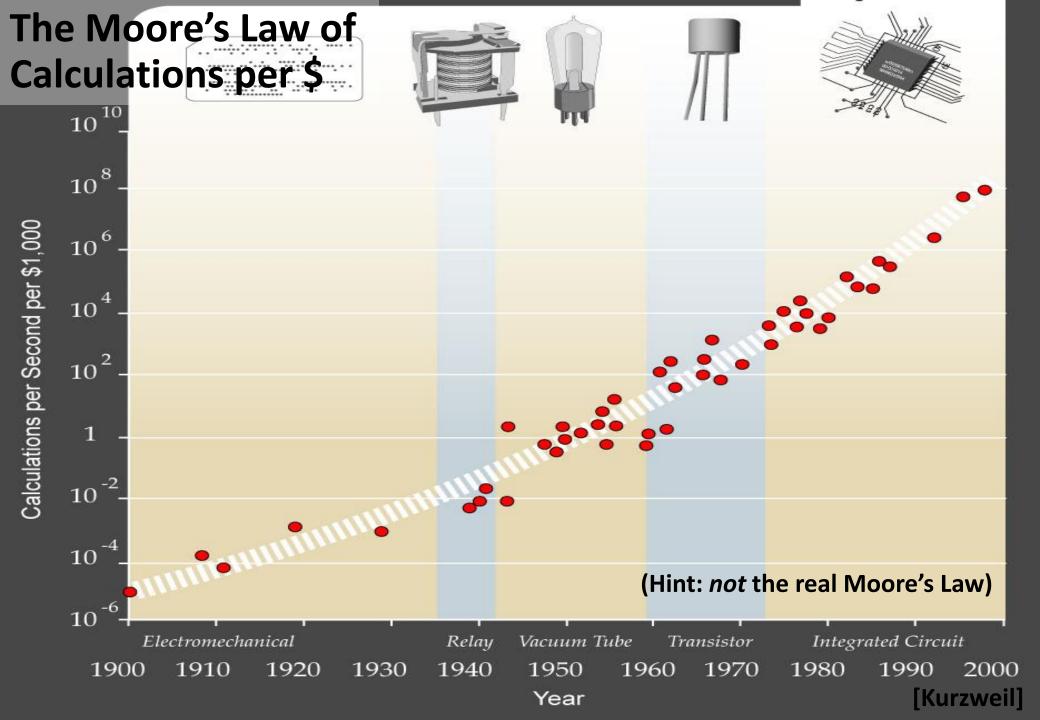

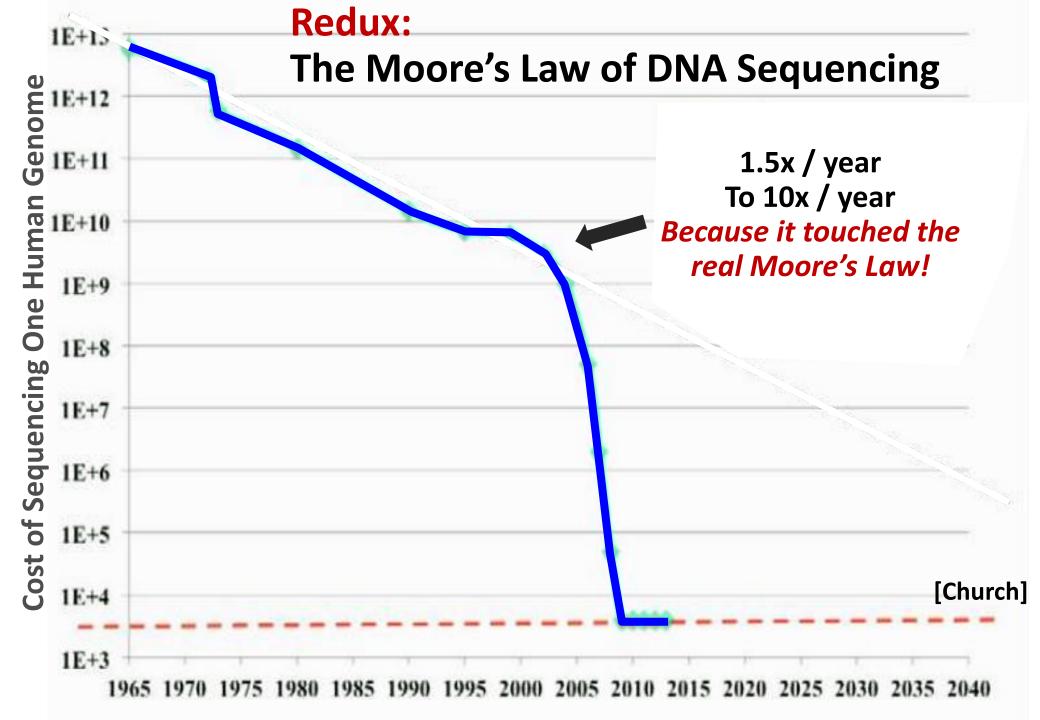

#### Will the Real Moore's Law Please Stand Up? (Please stand up)

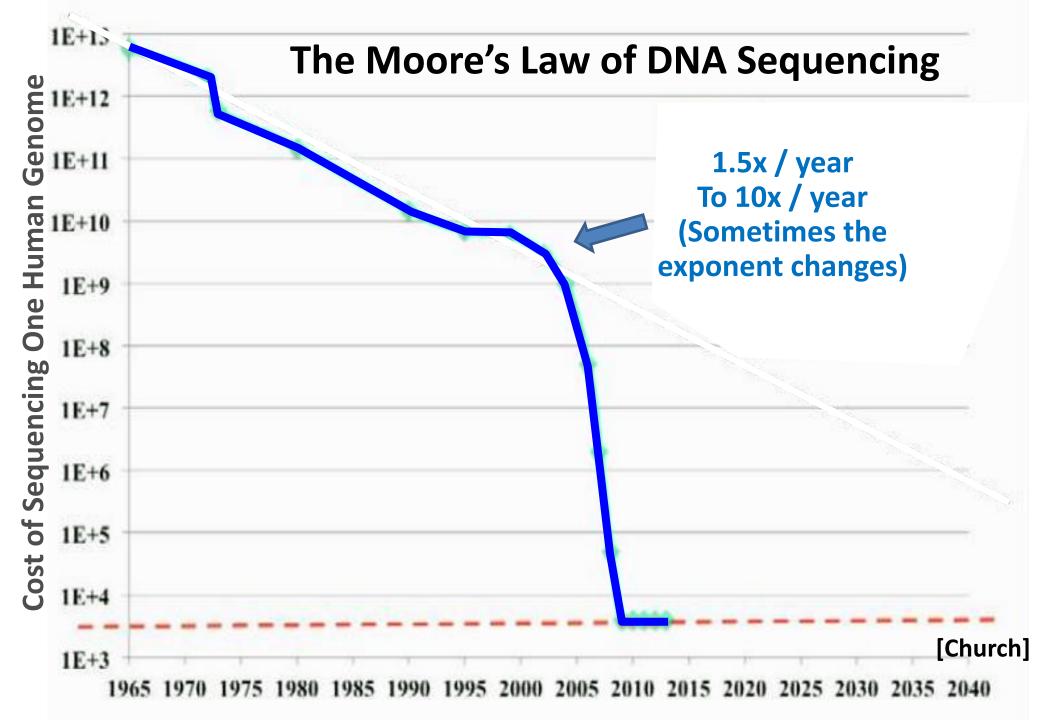

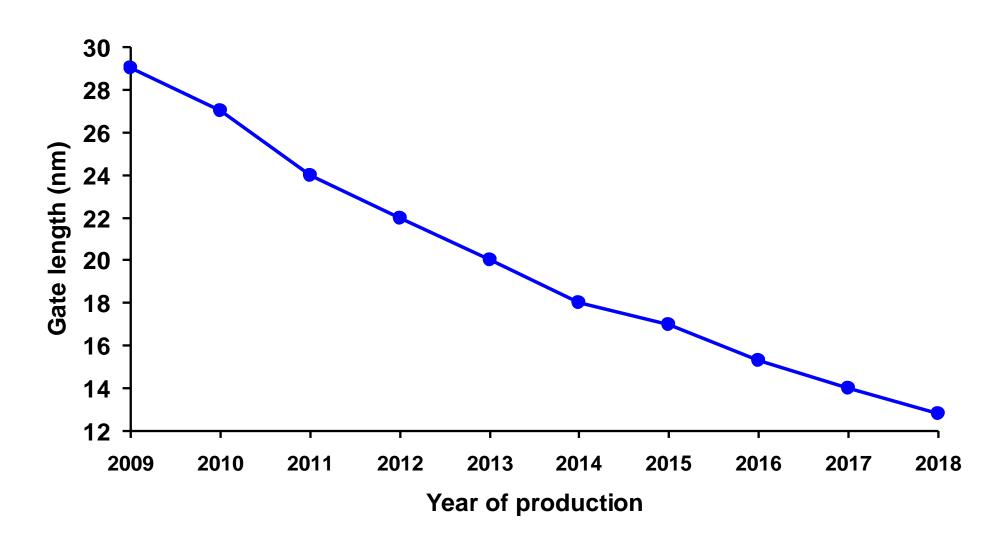

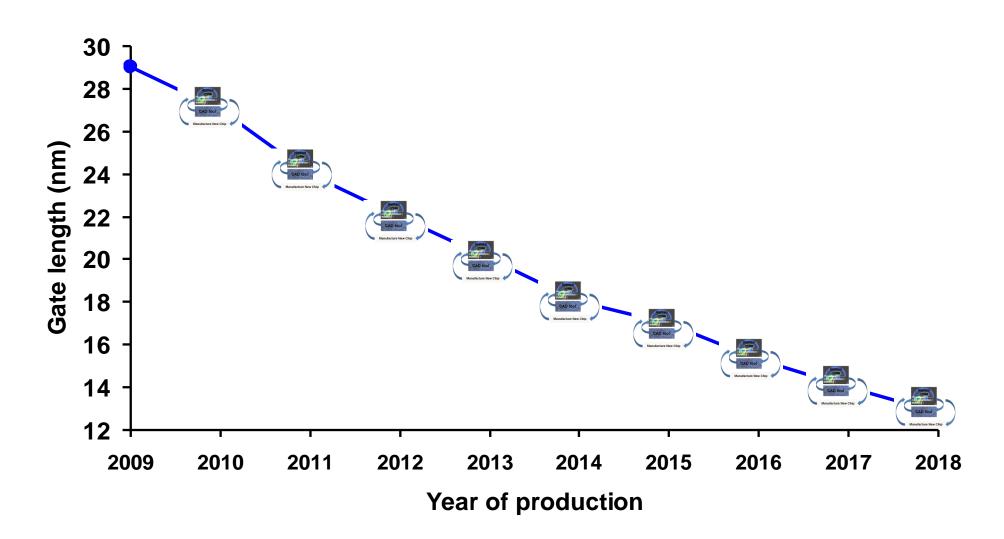

#### The Actual Moore's Law

(About *transistor size*.)

[International Technology Roadmap for Semiconductors, 2011]

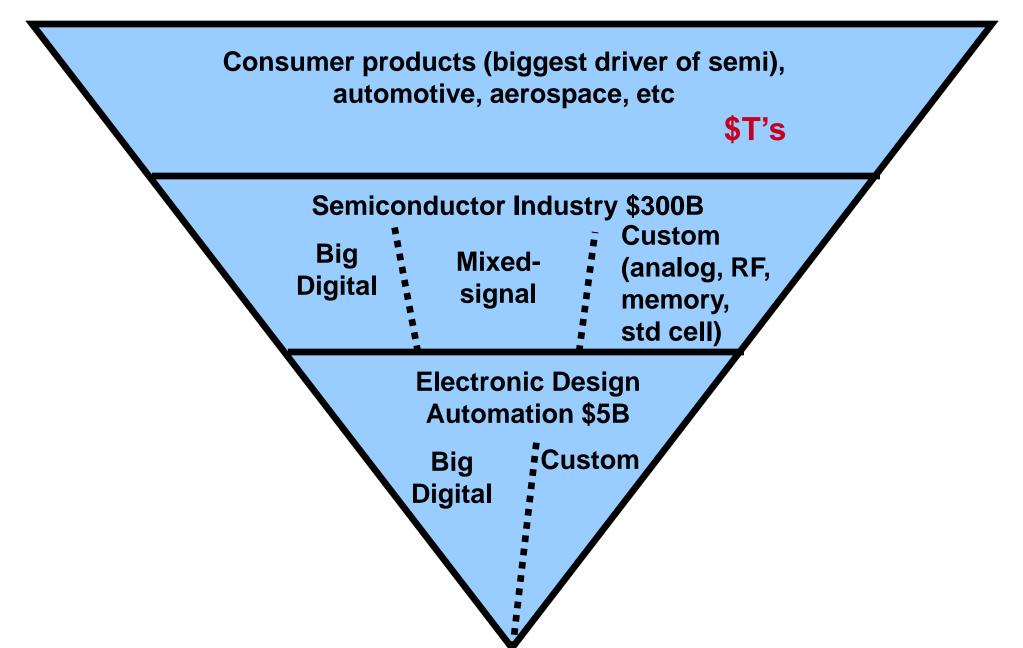

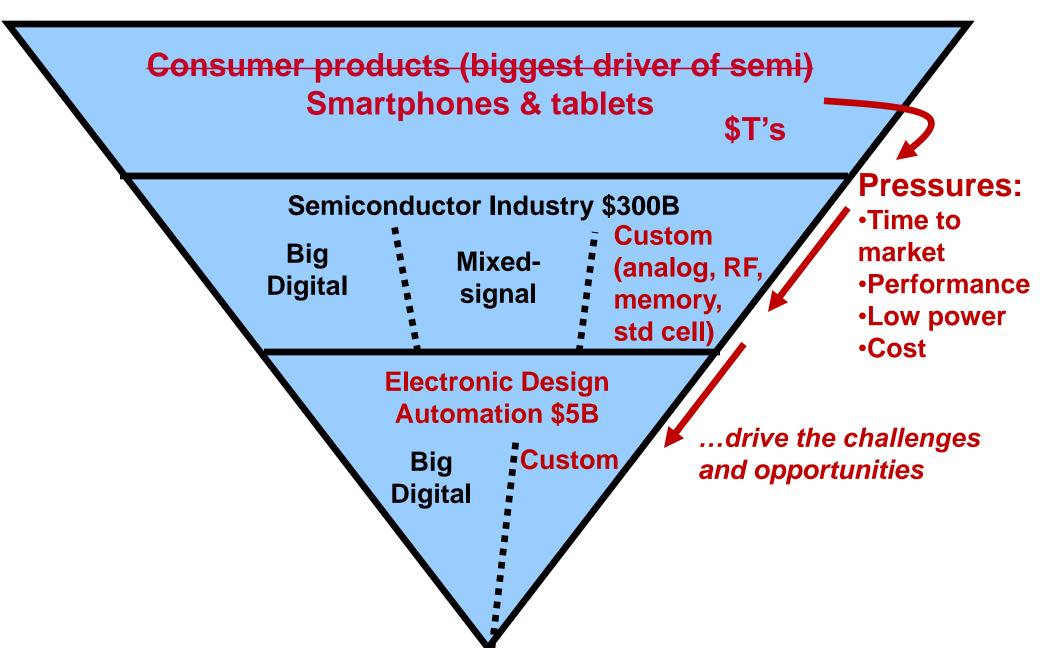

### *Why* Moore's Law?

#### **Market Motivations**

#### **Market Motivations**

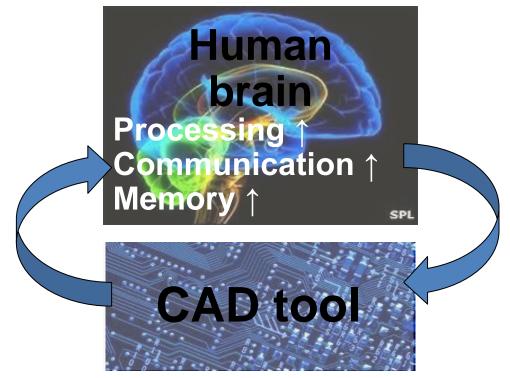

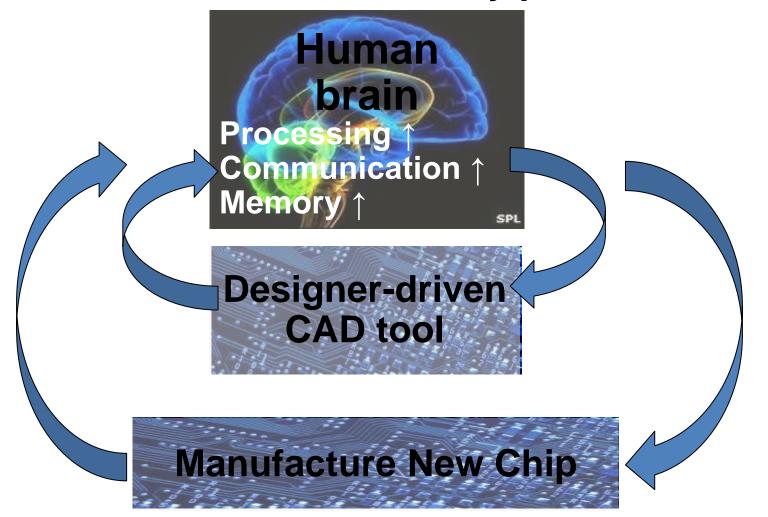

# Computer-aided design (CAD) tools cognitively enhance designers' abilities

Examples:

- Predict the effect of manufacturing

- Visualize circuit behavior

### BTW, I do CAD for a living

DeepChip Sept 27, 2013 – Solido ranked top 4 tool at DAC SemiWiki Sept 20, 2013 – Process variation is a yield killer DeepChip July 11, 2013 – DAC custom design trip report SemiWiki Jun 9, 2013 – First FinFETs manufactured at DAC SemiWiki May 28, 2013 – Solido on DAC Top 10 Must See List GarySmith May 21, 2013 – Solido on DAC Must See List SemiWiki May 18, 2013 – Solido on DAC Must See List SemiWiki May 18, 2013 – Solido CTO on Solido 6-sigma SemiWiki May 11, 2013 – Solido CTO on Solido 6-sigma SemiWiki May 11, 2013 – Solido CEO interview DeepChip May 2, 2013 – Solido SPICE simulation reduction SemiWiki Apr 27, 2013 – TSMC loves Solido DeepChip Mar 28, 2013 – User on custom design DeepChip Feb 1, 2013 – Solido ICCAD trip report More News & Events

Huawei-Histiicon for analog design Qualcomm for memory design Qualcomm for custom digital design TSMC for memory, std cell design TSMC for analog/RF design GLOBALFOUNDRIES for analog/RF design GLOBALFOUNDRIES for memory design STARC for analog/RF design Analog/RF design Memory, standard cell, analog/RF design DAC 2013 2012 2011 2010 customer reviews Cooley variation panel at DAC Survey of 486 engineers on variation

#### DeepChip

"The most interesting tool I saw at DAC was Solido's toolset for variation analysis. The GUI and scripts can help designers do faster variation analysis."

-Anonymous User, DeepChip

#### See a Video Demo

Variation-Aware Custom

Design Bool

o Memory Design White Paper

Solido and TSMC Webinar Presentation

Cadence Virtuoso with Solido White Paper

Synopsys HSPICE with Solido White Paper

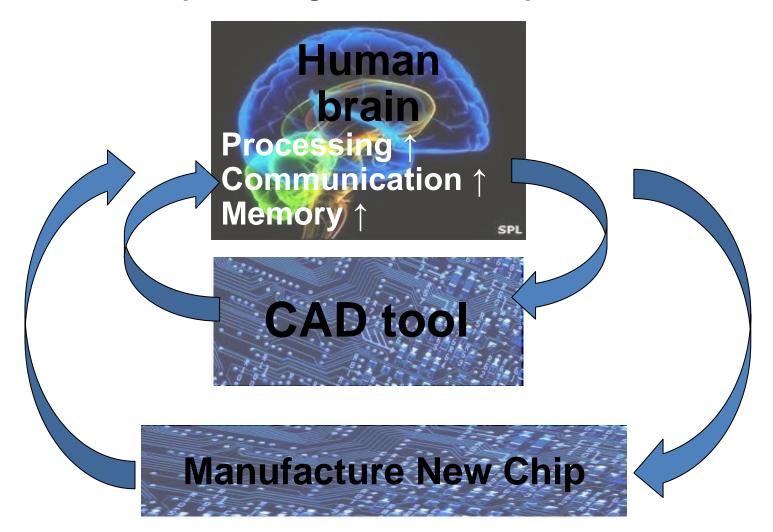

# Computer-aided design (CAD) tools cognitively enhance designers' abilities

Then we build a chip. We can use those chips to design on. It bootstraps!

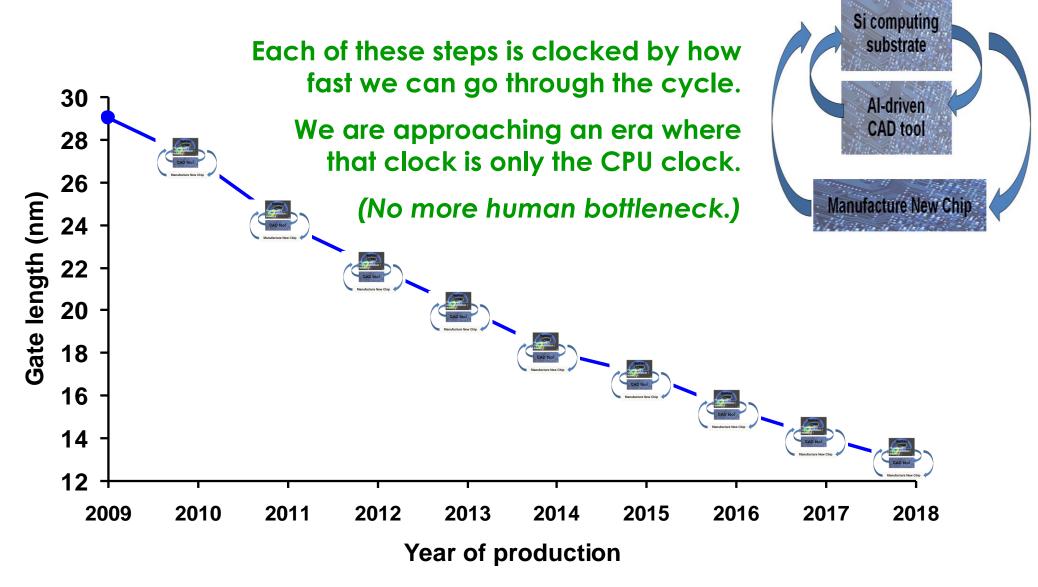

#### The Bootstrap

[ITRS, 2011]

### (Temporary) Barriers to Moore's Law

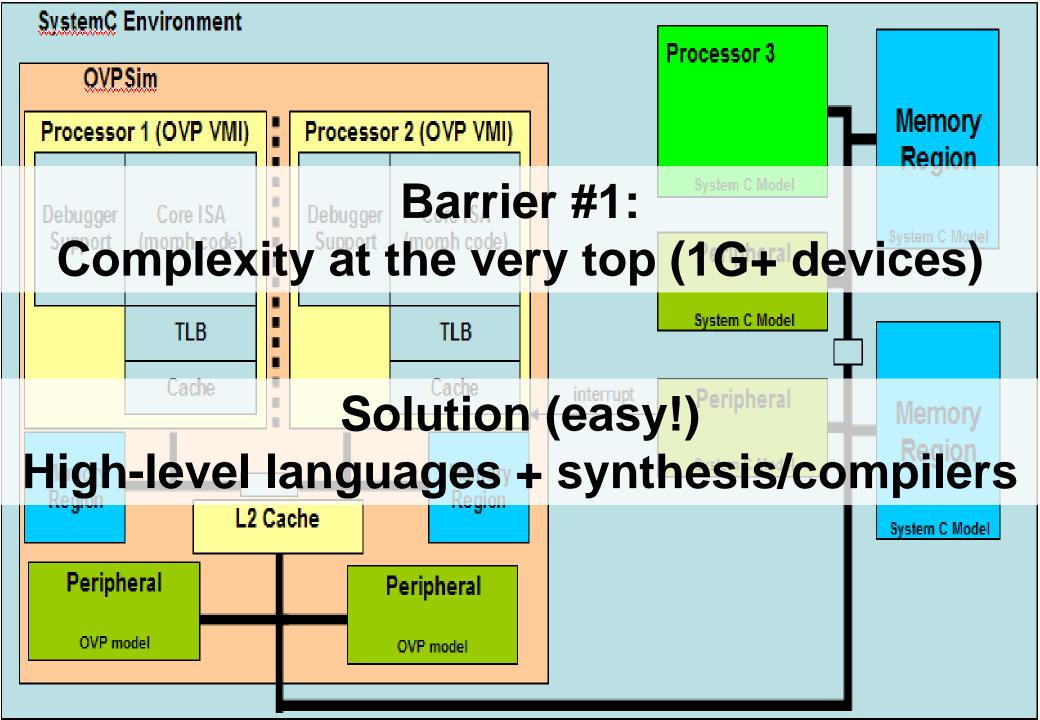

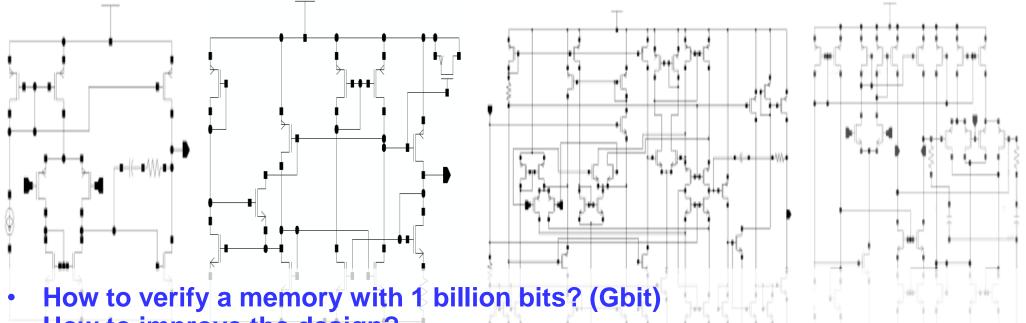

Barrier #1: Complexity at the very top (1G+ devices)

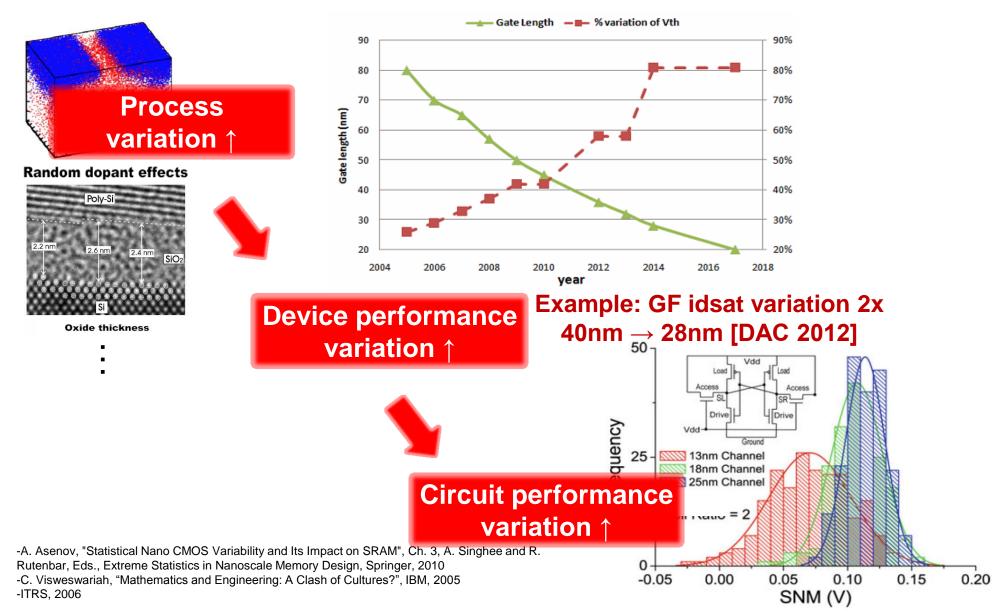

Barrier #2: Complexity at the very bottom: variation a.k.a. physics gone mad

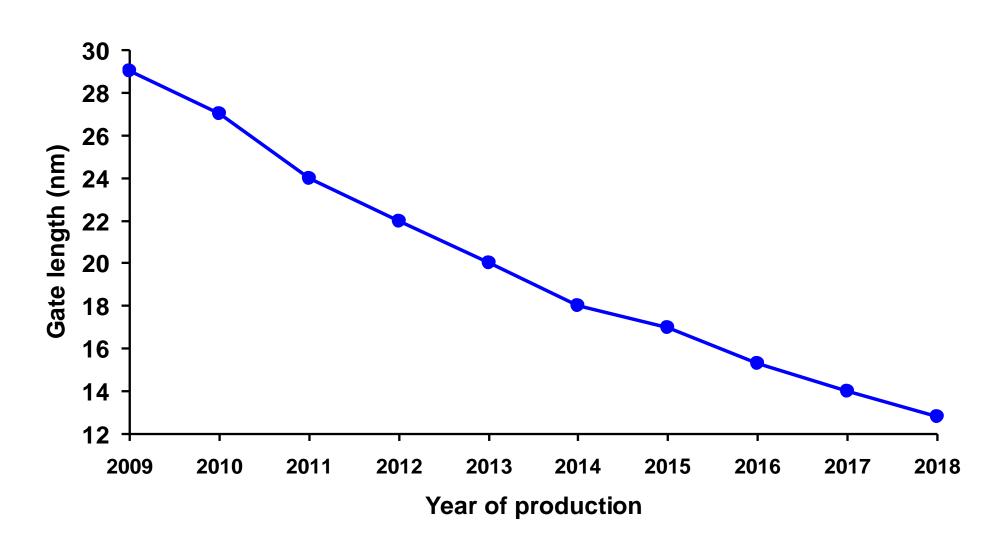

#### **Transistors Are Shrinking...**

[ITRS, 2011]

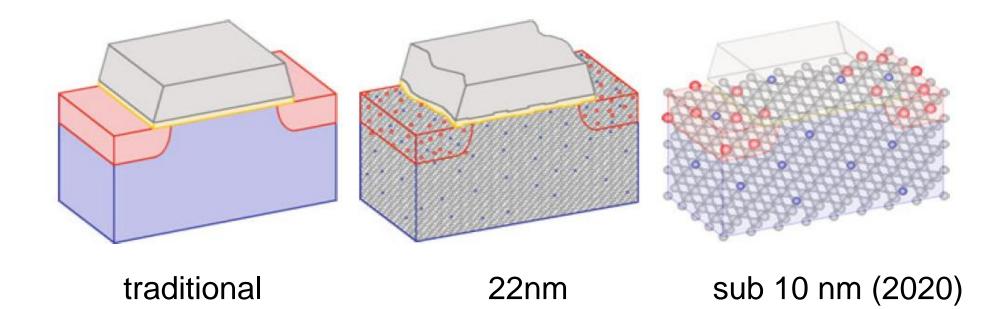

#### Transistors are shrinking But atoms aren't!

A. Asenov, "Statistical Nano CMOS Variability and Its Impact on SRAM", Chapter 3, A. Singhee and R. Rutenbar, Eds., Extreme Statistics in Nanoscale Memory Design, Springer, 2010

#### Variation = atoms out of place ...Propagating from devices to performance & yield

#### **Variability-Related Circuit Design Challenges**

- How to improve the design? (with variation gone wild)

- How to verify a PLL with 3375 PVT corners?

- How to improve the design? (with variation gone wild)

- To get lower power, lower delay, lower area, all in less time?

Barrier #2: Complexity at the very bottom: variation a.k.a. physics gone mad

## Solution: Traditional CAD tools?

# Q: Can (traditional) Computer-aided design (CAD) tools solve the variability problem?

A: No. Our brains cannot process all the information needed for design. (It's been tried).

Barrier #2: Complexity at the very bottom: variation a.k.a. physics gone mad

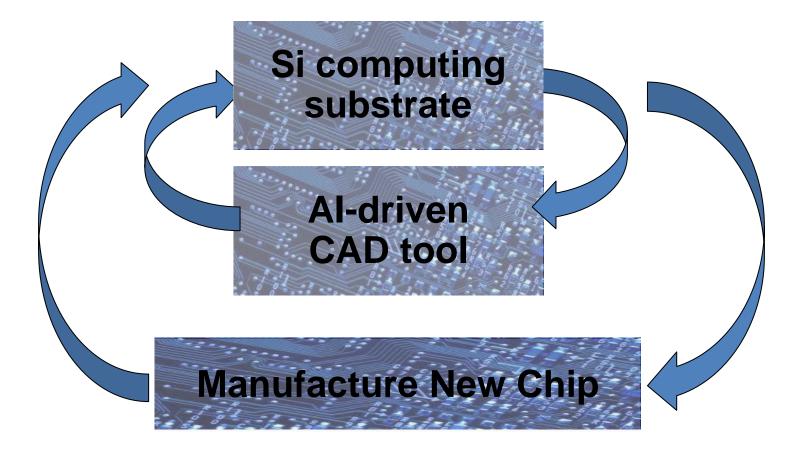

# Solution: Artificial Intelligence (AI)?

#### **Al-driven** Computer-aided design (CAD) tools

Solution: Al-driven CAD tool Al gets faster when the Si substrate faster. No more human bottleneck!

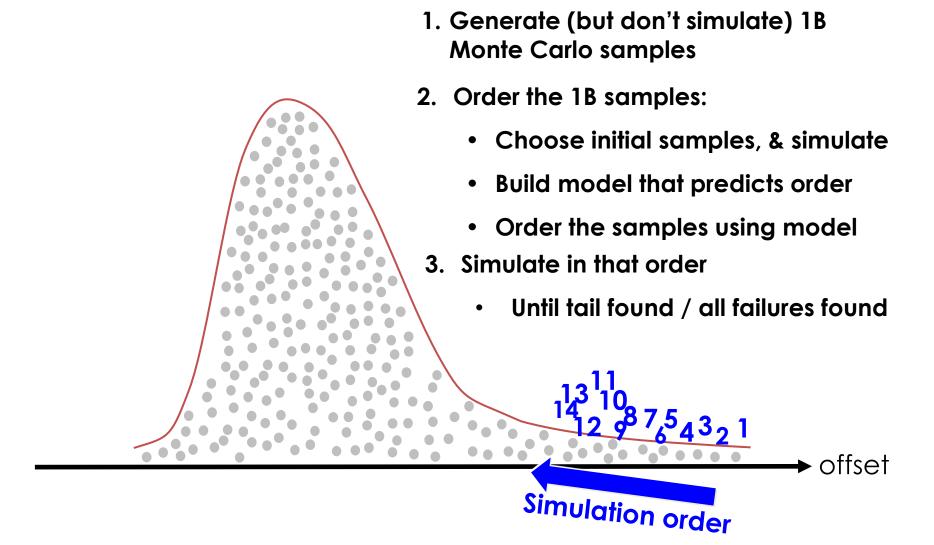

#### **Example: AI-Driven Variability-Aware Memory Design**

Interesting: many parallels with web search page-ranking

#### **Example: Al-driven "corners" analysis**

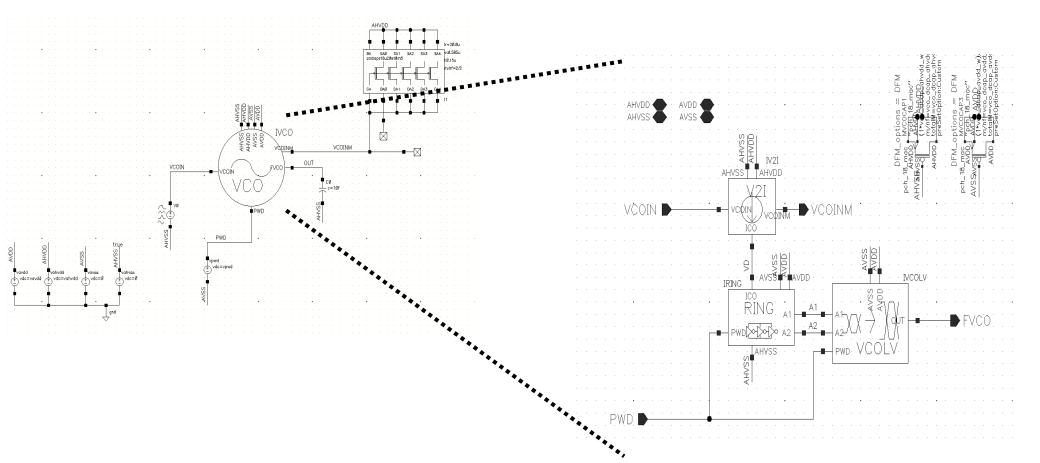

- TSMC 28nm, VCO of a PLL

- Specs: 48.3 < duty cycle < 51.7 %, 3 < Gain < 4.4GHz/V

- Traditional: 3375 PVT corners to simulate (temp, V<sub>ah,vdd</sub>, V<sub>a,vdd</sub>, V<sub>d,vdd</sub>, and 15 model sets)

- With AI: 275 corners to simulate, as thorough as before

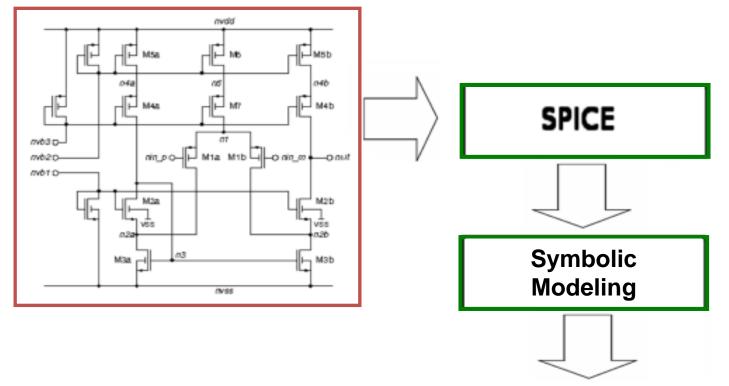

#### **Example: AI-based whitebox models of circuits**

| Perf.           | Expression                                                                                   |

|-----------------|----------------------------------------------------------------------------------------------|

|                 |                                                                                              |

| A <sub>LF</sub> | -10.3 + 7.08e-5 / id1                                                                        |

|                 | + 1.87 * In( -1.95e+9 + 1.00e+10 / (vsg1*vsg3)+ 1.42e+9 *(vds2*vsd5) / (vsg1*vgs2*vsg5*id2)) |

| $f_u$           | 10^( 5.68 - 0.03 * vsg1 / vds2 - 55.43 * id1+ 5.63e-6 / id1 )                                |

| PM              | 90.5 + 190.6 * id1 / vsg1 + 22.2 * id2 / vds2                                                |

| Voffset         | - 2.00e-3                                                                                    |

| SRp             | 2.36e+7 + 1.95e+4 * id2 / id1 - 104.69 / id2 + 2.15e+9 * id2 + 4.63e+8 * id1                 |

| SR <sub>n</sub> | - 5.72e+7 - 2.50e+11 * (id1*id2) / vgs2 + 5.53e+6 * vds2 / vgs2 + 109.72 / id1               |

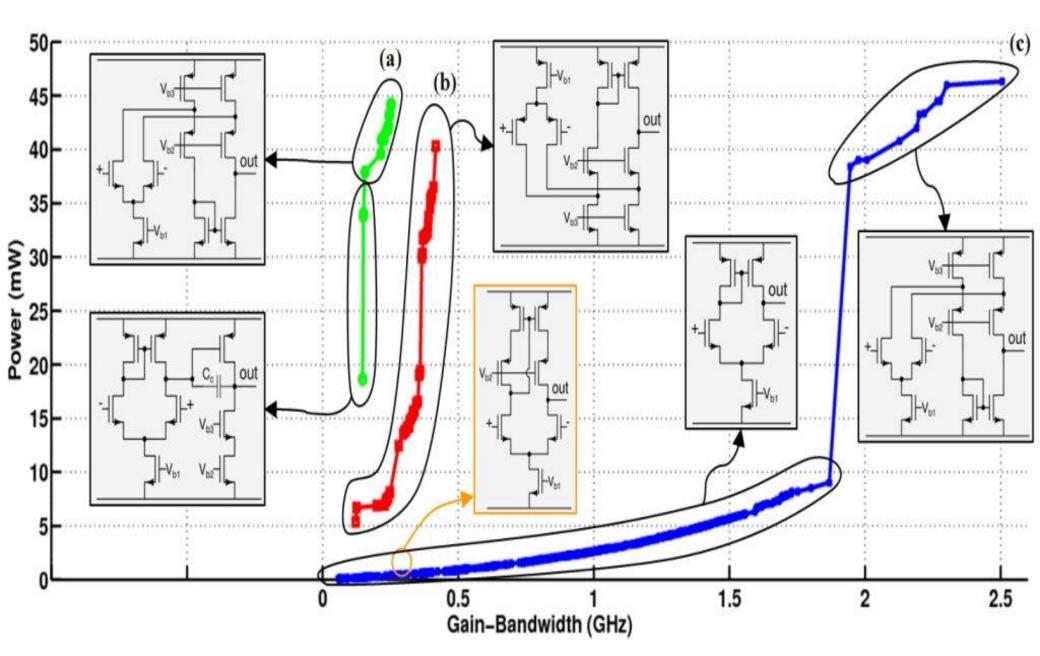

#### **Example: AI to synthesize analog circuit topologies**

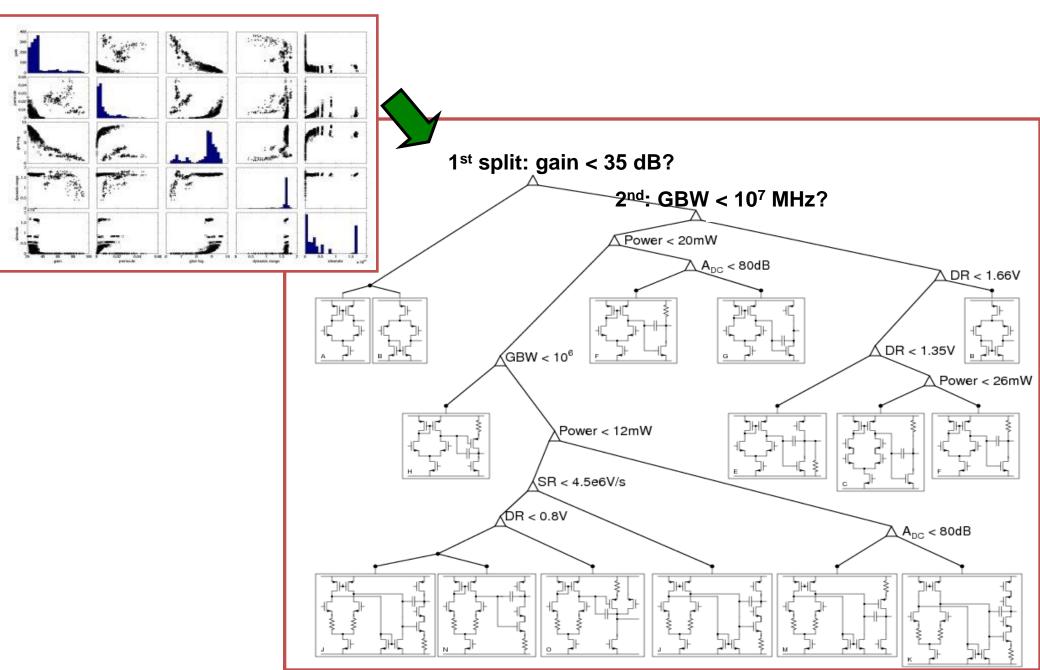

#### **Example: AI to generate decision trees**

# Some Al tools that I use for circuit design (and where else they're used)

- Classification Layout analysis, high-sigma analysis, Fraud detection, spam filtering ...

- Regression Circuit optimization, fast design sweep, high-sigma analysis, Stock prediction, sensitivity analysis ...

- Whitebox regression Behavioral modeling / system level simulation, Scientific discovery ...

- Optimization Worst-case PVT analysis, circuit cell optimization, airfoil design, circuit simulation ...

- Structural synthesis Analog topology synthesis, robotics ...

. . .

- System identification Behavioral modeling, Scientific discovery ...

- Ranking High-sigma analysis, Web search, ad serving, social discovery ...

- Control Behavioral modeling, Auto-driving autos, spacecraft trajectories ...

#### The Bootstrap, on Al steroids